ISMICT 2011– Montreux, Switzerland Workshop: Ultrasound dedicated to medical applications in the frame of the FP7 ICT European project ULTRAsponder

# Ultra-low power digital processing for medical applications

Marc MORGAN (marc.morgan@csem.ch)

System-on-Chip & Digital IC Design

Integrated & Wireless Systems Division

CSEM – Swiss Center for Electronics and Microtechnology

March 30, 2010

CSEM centre suisse d'électronique et de microtechnique

# **Quick introduction to CSEM**

- private company, founded in the 1980's

- not for profit

- approx. 400 employees on 5 sites in Switzerland, HQ in Neuchatel

- 8 technical divisions:

- microelectronics, photonics, nanotechnology, nanomedicine

- robotics, system engineering, microsystems, thin film optics

- approx. 60 MCHF annual budget

- over 20 start-ups and spin-offs since 1995

## **Medical applications**

- Ultrasound transponder implants

- Continuous ECG or multi-parameter monitoring

- Hearing aids

- Cochlear implants

- e-pills

- Other implants

- Common SoC requirements:

- extend battery life

- local processing

# **System-on-Chip for wireless applications**

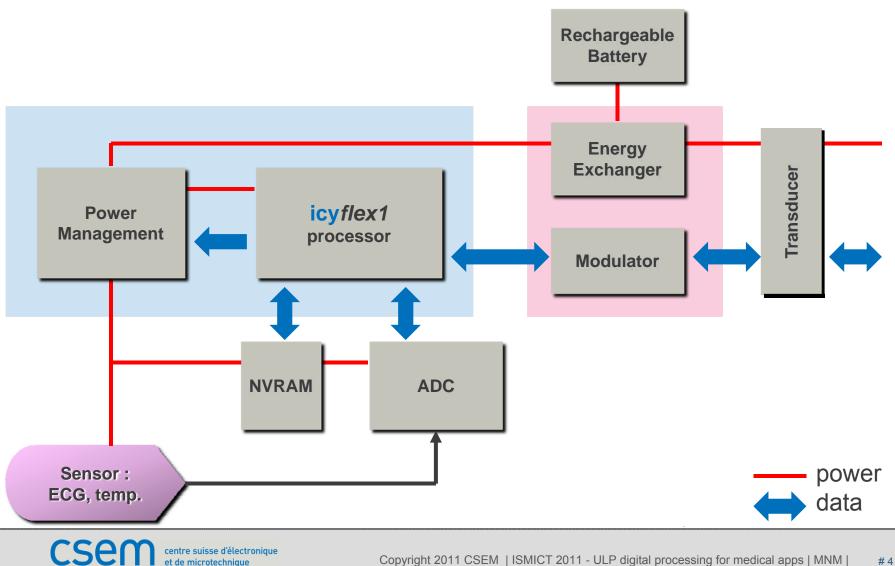

- <u>ULTRAsponder</u> SoC for ultrasound operation:

- ultra-low power processor + power management

- <u>icycom</u> for wireless sensor network:

- RF transceiver 863-928 MHz with OOK, FSK, OQPSK modulation

- TX: 40 mA, 10 dBm. RX: 3.5 mA, -100 dBm.

- e.g. 200 kb/s, MSK, range of 5 km (free space)

- 8-channel 10-bit ADC, 5 nC/sample

- <u>new SoC</u> for wireless Body Area Network:

- TX: 2.0 to 3.5 mA, -30 to -3 dBm.

RX: 3.5 mA, -100 dBm

- e.g. 200 kb/s, MSK, range of 0.1 to 2 km (free space)

#### The ULTRAsponder system view

et de microtechnique

Copyright 2011 CSEM | ISMICT 2011 - ULP digital processing for medical apps | MNM | #4

# The ULTRAsponder core SoC – digital functions

- Processor:

- icyflex1 ultra-low power DSP/control processor

- 120 µA/MHz at 1.0 V regulated power supply

- runs at up to 3.2 MHz at 1.0 V in this SoC

- SRAM: 96 kiBytes

- Other digital blocks:

- DMA controller, JTAG tap, IRQ controller, bus controller

- RTC, Timers, Watchdog, I2C, SPI, UART, GPIO

- Design For Test:

- 4 scan chains, Memory Built In Self Test

#### **The ULTRAsponder core SoC – power management**

- Power supply:

- 1.0 V 3.6 V

- Power management to supply power to the SoC and external devices

- programmable voltage regulator (64 steps, 0 VBAT)

- voltage divider by 2

- digital voltage regulator 1.0 V

- 2 voltage multipliers (2.7 V): max 10 µA and 13 mA currents

- separate power supply per bank of pads

#### The ULTRAsponder core SoC – power modes

| Mode        | Processor   | Digital<br>blocks | RAM<br>blocks | Clock   | Power               |

|-------------|-------------|-------------------|---------------|---------|---------------------|

| normal      | running     | all clocked       | all on        | 3.2 MHz | 120 μW/MHz<br>+ RAM |

| sleep       | clock gated | some clocked      | some on       | 3.2 MHz | 2-4 µW              |

| hibernation | power off   | only RTC on       | all off       | 32 kiHz | 1 µW                |

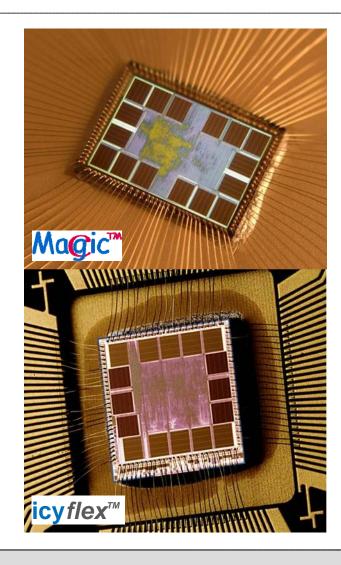

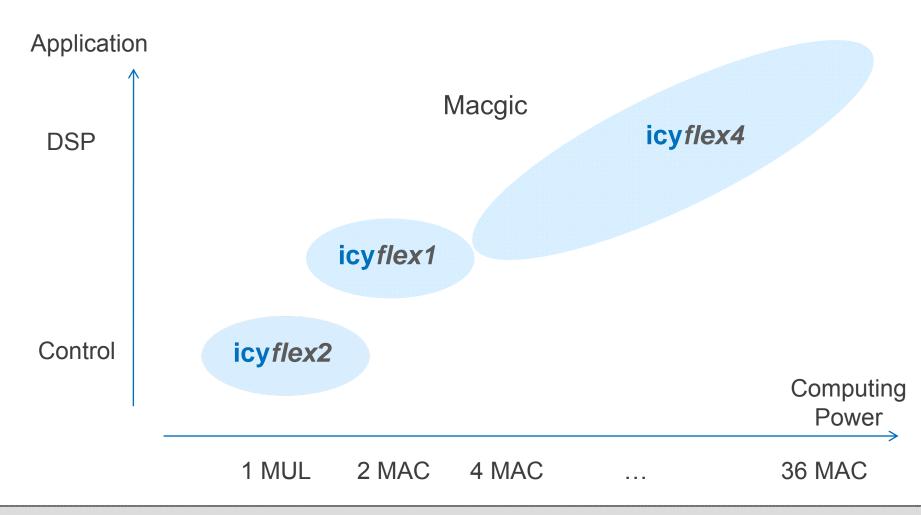

#### **Ultra low-power processors at CSEM**

- CSEM has a long history of designing low-power processors

- Watch processors: PUNCH (1993), µPUS, Combo (1982), ...

- CoolRISC, licensed to Semtech, Swatch group, TI, ...

- Powerful new processors with ultra low power consumption

- 2005: Macgic, a 16/24-bit DSP (4 MAC)

- 2006: **icyflex1**, a flexible processor for DSP/control applications

- 2009: icyflex2, a smaller processor for control applications

- 2009: icyflex4, a scalable processor for DSP/control applications

Macgic and icyflex are registered trademarks of CSEM

#### **Ultra-low power processors**

Macgic and the icyflex processors are optimized for power consumption:

- customizable (in VHDL)

- configurable (at run-time)

- architecture

- instruction set

- latch-based design

- clock-gating

### **Processor selection**

CSEM centre suisse d'électronique et de microtechnique

Copyright 2011 CSEM | ISMICT 2011 - ULP digital processing for medical apps | MNM | #10

# icyflex software development kit

- GNU C compiler (gcc) v 4.2.4

- icyflex instruction parallelism supported by latest releases of gcc

- libc and libm from RedHat's NewLib

- software implementation of IEEE floating-point standard

- GNU assembler / linker (binutils), v 2.20

- BFD / ELF32 object file format

- Binary, SREC, IHEX memory image file formats

- GNU debugger (gdb), v 6.7.1

- Mode 1: instruction set simulator of the icyflex core

- Mode 2: On-Chip Debug (OCD) through a JTAG interface

- icyflex instruction set simulator (ISS), written in C++

- Phase-accurate, pipelined

- Wrappers to SystemC, VHDL (Modelsim), Matlab/Simulink

- Eclipse integrated development environment, v Helios

- CDT C/C++ IDE plug-in

- icyflex plug-in

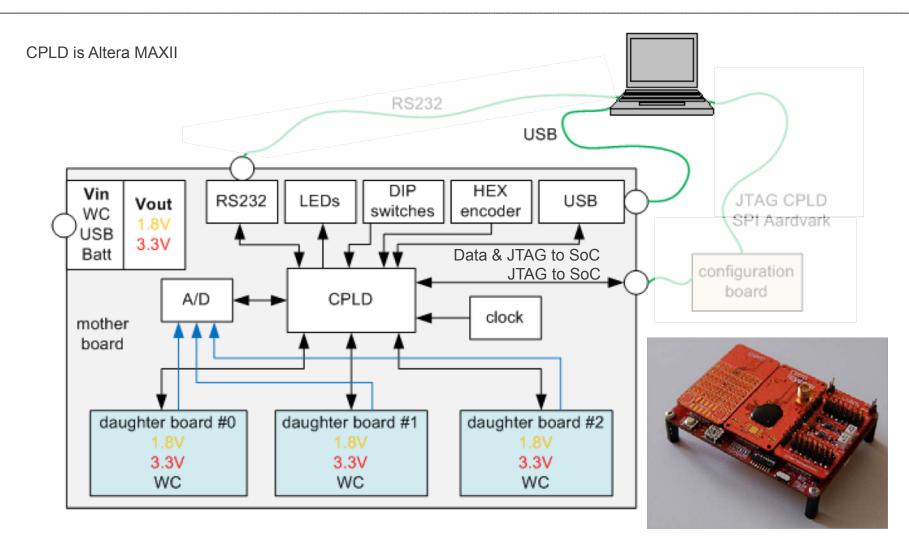

# icyflex hardware development kit

**CSEM** centre suisse d'électronique et de microtechnique

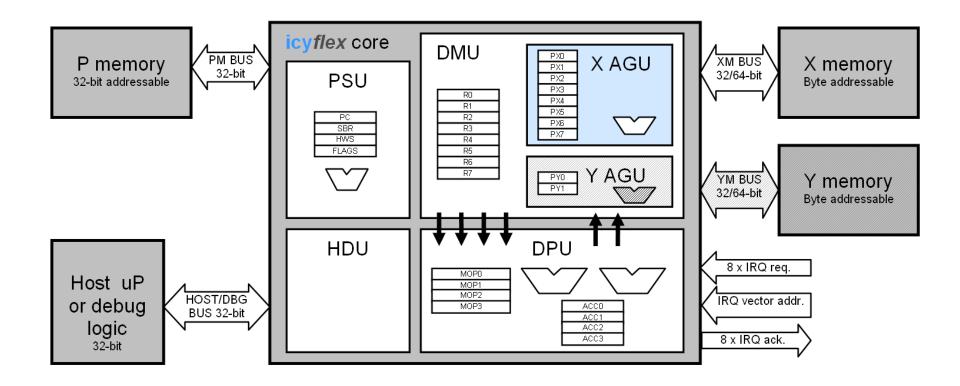

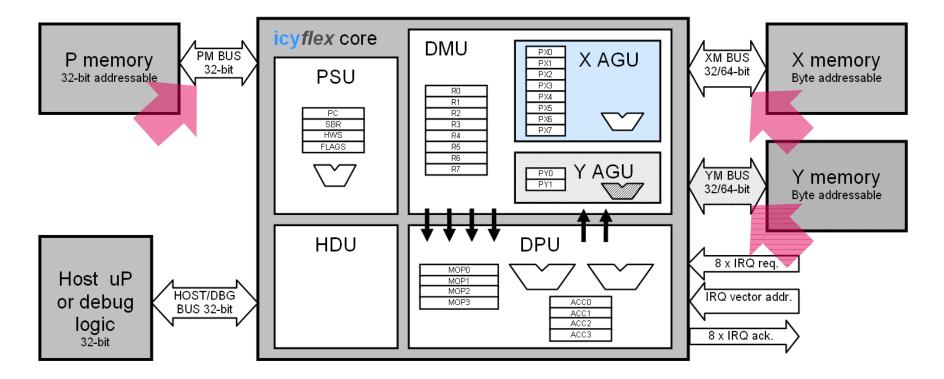

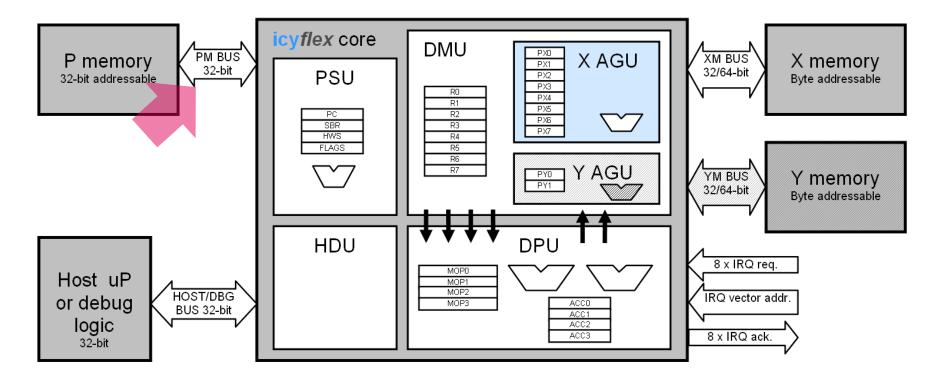

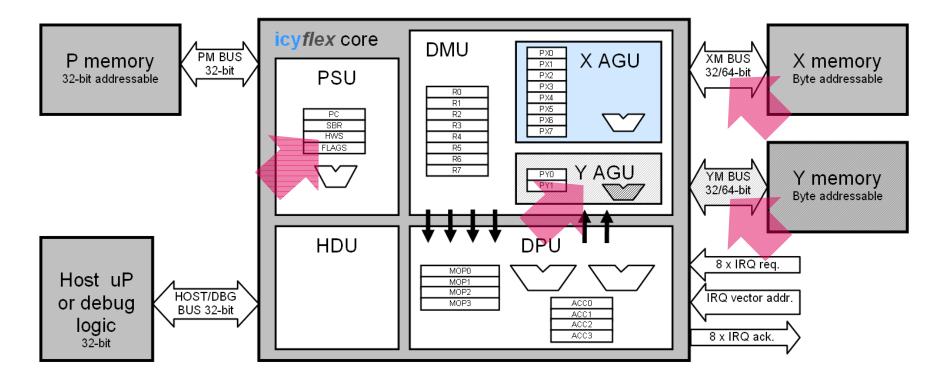

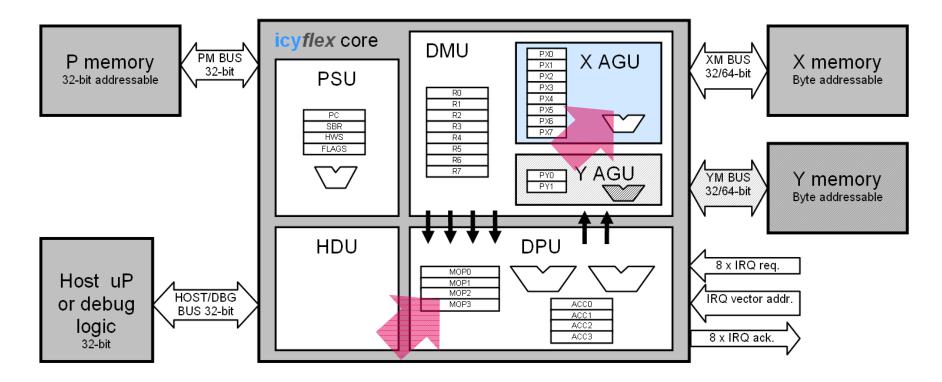

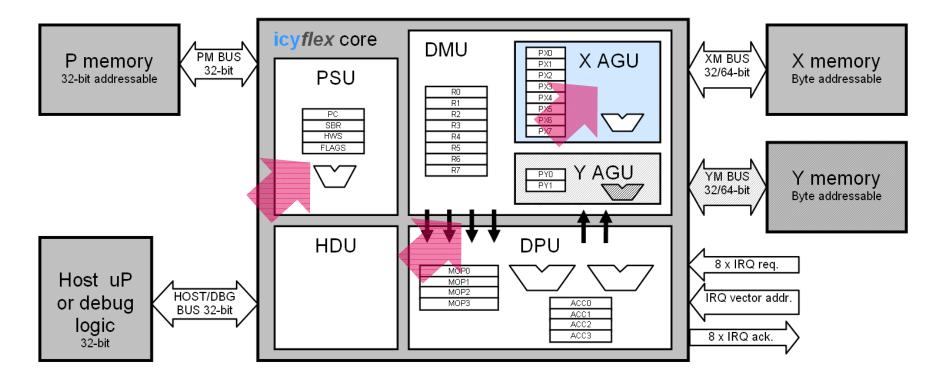

# **Overview of the icyflex1 processor**

# **Characteristics of the icyflex1 architecture**

- Simplicity

- 3-stage pipeline

- Efficiency → parallelism

- Data-level

- Instruction-level

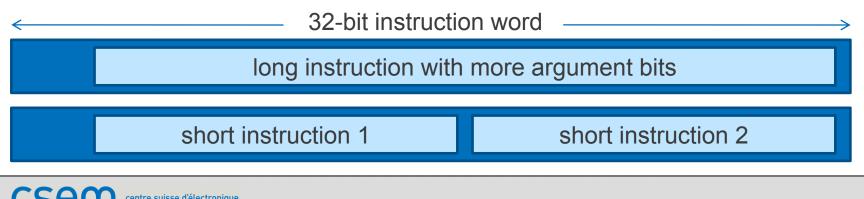

# **Characteristics of the icyflex1 architecture**

- Simplicity

- 3-stage pipeline

- Efficiency → parallelism

- Data-level:

- Two 32x32 multiply-accumulate units in parallel

- Instruction-level:

- Two short instructions can be executed in parallel

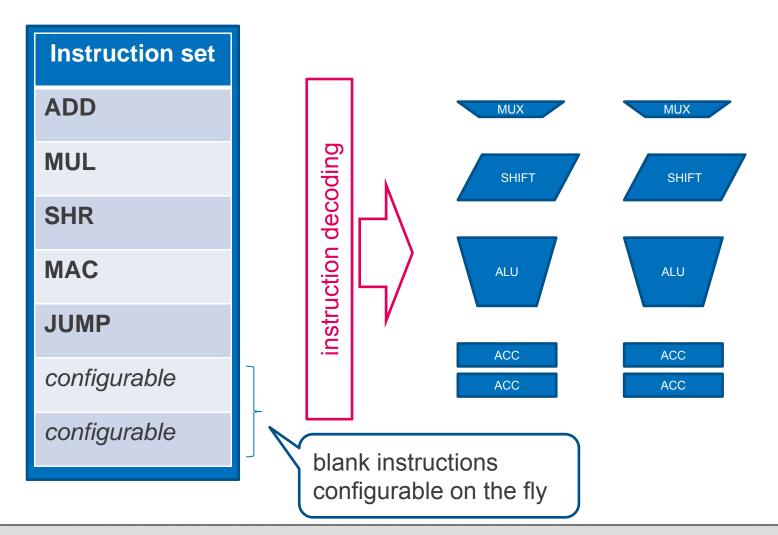

# **Characteristics of the icyflex1 architecture**

- Simplicity

- 3-stage pipeline

- Efficiency → parallelism

- Data-level:

- Two 32x32 multiply-accumulate units in parallel

- Instruction-level:

- Two short instructions can be executed in parallel

- New instructions can be configured at run-time

#### **Reconfigurable instructions and addressing modes**

CSEM centre suisse d'électronique et de microtechnique

3 separate busses  $\rightarrow$  up to 3 parallel accesses every clock cycle less clock cycles  $\rightarrow$  less power consumption

32-bit instruction word  $\rightarrow$  optimized instruction set avoids VLIW shorter instruction word  $\rightarrow$  less power consumption

customizable at synthesis  $\rightarrow$  busses can be shrunk, blocks can be removed only useful logic is integrated  $\rightarrow$  less power consumption

reconfigurable instructions and addressing modes → execute less instructions

→ less clock cycles, smaller program memory, less power consumption

DSP-type features: zero-overhead hardware loop, complex addressing modes, high and balanced throughput

#### **Performance summary**

|                        |                     | icy <i>flex1</i> | icy <i>flex</i> 2 | icy <i>flex4</i> |

|------------------------|---------------------|------------------|-------------------|------------------|

| MAC (or MUL)           | units               | 2                | (1)               | 4 + 4 VPS        |

| Data size [bits]       |                     | 16/32            | 16/32             | 16/32            |

| Pipeline depth         |                     | 3                | 5                 | 5-8              |

| Software tools         |                     | gcc / gas        | gcc/gas           | gcc / gas        |

| k Gates                |                     | 110              | 40                | 130 + 90 VPS     |

| Max. ops/cycle         |                     | 16               | 6                 | 33 + 31 VPS      |

| Max. freq.<br>[MHz]    | 180 nm              | 50               |                   |                  |

|                        | lp rvt <b>90 nm</b> |                  | 180               | 180              |

| Avg. Power<br>[µW/MHz] | 180 nm              | 120              | 30                |                  |

|                        | 65 nm               |                  | 6                 | 10 to 150*       |

|                        |                     |                  |                   |                  |

\*) VPS=2, FFT radix-4 64 points

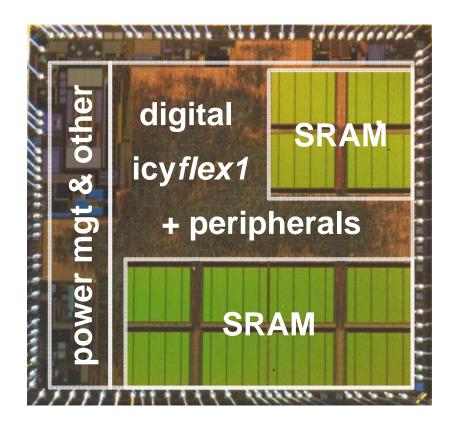

# The Ultrasponder core SoC

- Integrated in TSMC 180 nm generic CMOS process

- 5 x 5 mm<sup>2</sup>

- 12 blocks of 8 kiB ultra-low power SRAM

- mix of thin and thick gate transistors

# part of the research which went into the development of the ULTRAsponder system-on-chip was funded by the European Community's Seventh Framework Programme (FP7/2007-2013)

# Thank you for your attention!

Questions?

Contact: marc.morgan@csem.ch

CSEM centre suisse d'électronique et de microtechnique